# Digital Logic Design: a rigorous approach © Chapter 16: Signed Addition

Guy Even Moti Medina

School of Electrical Engineering Tel-Aviv Univ.

January 24, 2013

Book Homepage: http://www.eng.tau.ac.il/~guy/Even-Medina

### Preliminary questions

- How are signed integers represented in a computer?

- When the signed integers added and subtracted in a computer?

- Can we use the same circuitry for adding unsigned and signed integers?

### Representation of negative integers

#### Definition

The number represented in sign-magnitude representation by  $A[n-1:0] \in \{0,1\}^n$  and  $S \in \{0,1\}$  is

$$(-1)^{S} \cdot \langle A[n-1:0] \rangle.$$

#### Definition

The number represented in one's complement representation by  $A[n-1:0] \in \{0,1\}^n$  is

$$-(2^{n-1}-1)\cdot A[n-1] + \langle A[n-2:0]\rangle.$$

#### Definition

The number represented in two's complement representation by  $A[n-1:0] \in \{0,1\}^n$  is

$$-2^{n-1} \cdot A[n-1] + \langle A[n-2:0] \rangle.$$

### Comparison between representation methods

| binary string $ec{X}$ | $\langle \vec{X}  angle$ | 2's comp | 1's comp | sign-mag |  |

|-----------------------|--------------------------|----------|----------|----------|--|

| 000                   | 0                        | 0        | 0        | +0       |  |

| 001                   | 1                        | 1        | 1        | 1        |  |

| 010                   | 2                        | 2        | 2        | 2        |  |

| 011                   | 3                        | 3        | 3        | 3        |  |

| 100                   | 4                        | -4       | -3       | -0       |  |

| 101                   | 5                        | -3       | -2       | -1       |  |

| 110                   | 6                        | -2       | -1       | -2       |  |

| 111                   | 7                        | -1       | 0        | -3       |  |

- symmetric range: one's complement and sign-magnitude.

- two representations for zero: one's complement and sign-magnitude.

### Range of representable numbers

We denote the number represented in two's complement representation by A[n-1:0] as follows:

$$[A[n-1:0]] \stackrel{\triangle}{=} -2^{n-1} \cdot A[n-1] + \langle A[n-2:0] \rangle.$$

We denote the set of signed numbers that are representable in two's complement representation using n-bit binary strings by  $T_n$ .

#### Claim

$$T_n = \left\{-2^{n-1}, -2^{n-1} + 1, \dots, 2^{n-1} - 1\right\}.$$

### Computing a two's complement representation

**Algorithm 1** two-comp(x, n) - An algorithm for computing the two's complement representation of x using n bits.

- ① If  $x \notin T_n$  return (fail).

- ② If  $x \ge 0$  return  $(0 \circ bin_{n-1}(x))$ .

- **3** If x < 0 return  $(bin_n(x + 2^n))$ .

## Computing a two's complement representation

### Example

$$T_4 = \left\{-2^3, -2^3 + 1, \dots, 2^3 - 1\right\}.$$

Hence.

two-comp(8,4) = fail,

two-comp(5,4) =

$$(0 \circ bin_3(5)) = 0101$$

,

two-comp(-6,4) =  $(bin_4(-6+2^4)) = 1010$ ,

two-comp(-1,4) =  $(bin_4(-1+2^4)) = 1111$ .

### Negation in two's complement representation

The following claim deals with negating a value represented in two's complement representation.

#### Claim

$$-[A[n-1:0]] = [INV(A[n-1:0])] + 1.$$

Examples:  $\vec{A} = 0110$  and  $\vec{A} = 1001$ .

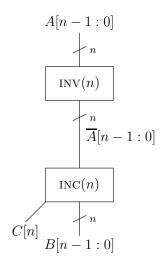

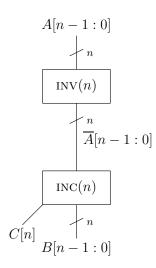

# Negation based on

$$-[A[n-1:0]] = [INV(A[n-1:0])] + 1$$

### Negation based on

$$-[A[n-1:0]] = [INV(A[n-1:0])] + 1$$

- We compute  $\langle \overline{A[n-1:0]} \rangle + 1$ .

- But need |A[n-1:0]| + 1.

- So  $\langle C[n] \cdot B[n-1:0] \rangle =$  $\langle A[n-1:0]\rangle + 1.$

- Does  $\left[ \vec{B} \right] = \left[ \vec{A} \right]$ ?

- Suspect C[n] = 1! Assume C[n] = 0...

- So  $\langle B[n-1:0]\rangle = \langle \overline{A[n-1:0]}\rangle + 1.$

- $[B[n-1:0]] = \overline{A[n-1:0]} + 1?$

### Negation

- Very easy in sign-magnitude representation.

- Easy in one's-complement representation.

- In two's complement representation: need to check that  $-\left[\vec{A}\right]\in\mathcal{T}_{n}...$

- Still, we need a proof and a way to tell when we fail.

### Alternative definition

#### Claim

For every

$$A[n-1:0] \in \{0,1\}^n$$

$$\operatorname{mod}(\langle \vec{A} \rangle, 2^n) = \operatorname{mod}(\left\lceil \vec{A} \right\rceil, 2^n).$$

### Example

Let n = 4 and let A[3:0] = 0110, B[3:0] = 1001, then:

$$\langle A[3:0] \rangle = 6$$

,  $[A[3:0]] = 6$ ,  $\langle B[3:0] \rangle = 9$ ,  $[B[3:0]] = -7$ .

Hence,

$$\begin{split} \langle \vec{A} \rangle - \left[ \vec{A} \right] &= 6 - 6 = 0 = 0 \text{ (mod } 2^4) \;, \\ \langle \vec{B} \rangle - \left[ \vec{B} \right] &= 9 - (-7) = 16 = 0 \text{ (mod } 2^4) \;. \end{split}$$

### Sign bit

The most significant bit A[n-1] of a string A[n-1:0] that represents a two's complement number is often called the sign-bit of  $\vec{A}$ . The following claim justifies this term.

#### Claim

$$[A[n-1:0]] < 0 \iff A[n-1] = 1.$$

Do not be misled by the term sign-bit. Computing the absolute value of  $\begin{bmatrix} \vec{A} \end{bmatrix}$  requires negation... Example:  $\vec{A}=1111$  and  $\vec{A}=0111$ .

### Sign extension.

Duplicating the most significant bit does not affect the value represented in two's complement representation. This is similar to padding zeros from the left in binary representation.

#### Claim

If

$$A[n] = A[n-1]$$

, then

$$[A[n:0]] = [A[n-1:0]].$$

### Corollary

$$[A[n-1]^* \circ A[n-1:0]] = [A[n-1:0]].$$

### Example:

$$[111111111111111111111] = [10] = -2$$

$[111111111111111111111] = [1] = -1$

### Reduction: two's complement addition to binary addition

Goal: two's complement addition

$$\left[\vec{A}\right] + \left[\vec{B}\right] + C[0].$$

Suppose:

$$A[n-1:0], B[n-1:0], S[n-1:0] \in \{0,1\}^n$$

$C[0], C[n] \in \{0,1\}$

satisfy

$$\langle A[n-1:0]\rangle + \langle B[n-1:0]\rangle + C[0] = \langle C[n] \cdot S[n-1:0]\rangle. \quad (1)$$

• When does the output S[n-1:0] satisfy:

$$|\vec{S}| = [A[n-1:0]] + [B[n-1:0]] + C[0]?$$

(2)

• How can we know that Equation 2 holds?

# Reduction of two's comp addition to binary addition

#### Theorem

Let C[n-1] denote the carry-bit in position [n-1] associated with the binary addition described in Equation 1 and let

$$z \stackrel{\triangle}{=} [A[n-1:0]] + [B[n-1:0]] + C[0].$$

Then,

$$C[n] - C[n-1] = 1 \implies z < -2^{n-1}$$

(3)

$$C[n-1] - C[n] = 1 \implies z > 2^{n-1} - 1$$

(4)

$$z \in T_n \iff C[n] = C[n-1]$$

(5)

$$z \in T_n \implies z = [S[n-1:0]].$$

(6)

# Example

| [ <i>A</i> [3 : 0]]   | -3 | -4        | -6 | 7         |

|-----------------------|----|-----------|----|-----------|

| [ <i>B</i> [3 : 0]]   | -5 | -5        | 5  | 1         |

| C[0]                  | 1  | 0         | 0  | 1         |

| <i>C</i> [ <i>n</i> ] | 1  | 1         | 1  | 0         |

| C[n-1]                | 1  | 0         | 1  | 1         |

| [S[n-1:0]]            | -7 | 7         | -1 | <b>-7</b> |

| Z                     | -7 | <b>-9</b> | -1 | 9         |

### Detecting overflow

Overflow - the sum of signed numbers is not in  $T_n$ .

#### Definition

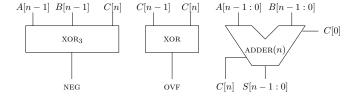

Let  $z \stackrel{\triangle}{=} [A[n-1:0]] + [B[n-1:0]] + C[0]$ . The signal OVF is defined as follows:

$$ext{OVF} \stackrel{\triangle}{=} egin{cases} 1 & ext{if } z

otin T_n \\ 0 & ext{otherwise}. \end{cases}$$

the term "out-of-range" is more appropriate than "overflow" (which suggests that the sum is too big). Favor tradition... By the theorem

OVF =

$$XOR(C[n-1], C[n])$$

.

### Determining the sign of the sum

#### Definition

The signal NEG is defined as follows:

$$_{\mathrm{NEG}}\stackrel{\triangle}{=} egin{cases} 1 & \mathrm{if}\ z < 0 \ 0 & \mathrm{if}\ z \geq 0. \end{cases}$$

brute force method:

NEG =

$$\begin{cases} S[n-1] & \text{if no overflow} \\ 1 & \text{if } C[n] - C[n-1] = 1 \\ 0 & \text{if } C[n-1] - C[n] = 1. \end{cases}$$

(7)

#### Claim

$$NEG = XOR_3(A[n-1], B[n-1], C[n]).$$

### A two's-complement adder

#### Definition

A two's-complement adder with input length n is a combinational circuit specified as follows.

Input:

$$A[n-1:0], B[n-1:0] \in \{0,1\}^n$$

, and  $C[0] \in \{0,1\}$ .

Output:

$$S[n-1:0] \in \{0,1\}^n$$

and NEG, OVF  $\in \{0,1\}$ .

Functionality: Define z as follows:

$$z \stackrel{\triangle}{=} [A[n-1:0]] + [B[n-1:0]] + C[0].$$

The functionality is defined as follows:

$$z \in T_n \implies [S[n-1:0]] = z$$

$z \in T_n \iff \text{OVF} = 0$

$z < 0 \iff \text{NEG} = 1.$

We denote a two's-complement adder by S-ADDER(n).

# A two's complement adder S-ADDER(n)

In an arithmetic logic unit (ALU), one may use the same circuit for signed addition and unsigned addition.

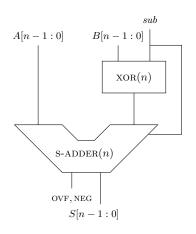

### A two's complement adder/subtractor

#### **Definition**

A two's-complement adder/subtractor with input length n is a combinational circuit specified as follows.

Input:

$$A[n-1:0], B[n-1:0] \in \{0,1\}^n$$

, and  $sub \in \{0,1\}$ .

Output:

$$S[n-1:0] \in \{0,1\}^n$$

and NEG, OVF  $\in \{0,1\}$ .

Functionality: Define z as follows:

$$z \stackrel{\triangle}{=} [A[n-1:0]] + (-1)^{sub} \cdot [B[n-1:0]].$$

The functionality is defined as follows:

$$z \in T_n \implies [S[n-1:0]] = z$$

$z \in T_n \iff \text{OVF} = 0$

$z < 0 \iff \text{NEG} = 1.$

We denote a two's-complement adder/subtractor by ADD-SUB(n).

# An implementation of an ADD-SUB(n)

### Claim

The implementation of ADD-SUB(n) is correct.

### Summary

- three ways for representing negative integers: sign-magnitude, one's-complement, and two's complement. We then focused on two's complement representation.

- Negating.

- Properties of two's complement representation: (i) modulo 2<sup>n</sup> congruent to binary rep. (ii) sign bit. (iii) sign-extension.

- Reduce the task of two's complement addition to binary addition, and: (i) overflow detection (ii) sign of the sum even if an overflow occurs.

- Implementation of a circuit of adder/subtractor (basic part in ALU).