#### **Circuit Topologies & Analysis Techniques in HF ICs**

1

#### Outline

•Analog vs. Microwave Circuit Design

- Impedance matching

- Tuned circuit topologies

- Techniques to maximize bandwidth

- •Challenges in differential HF circuits

- Nonlinear Techniques

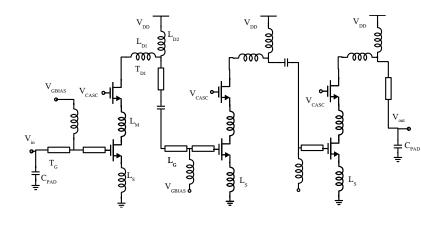

### **Typical HF IC Topologies: inductors**

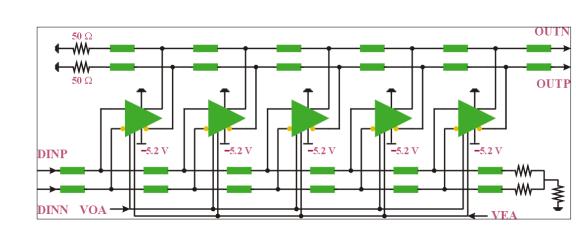

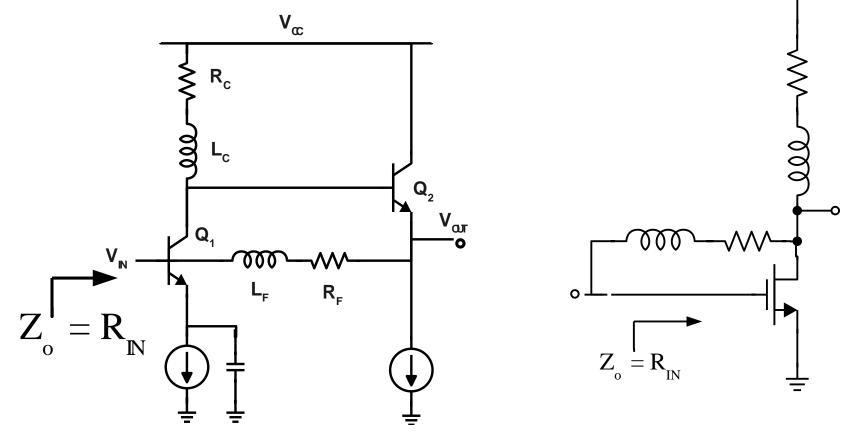

**Broadband High-speed Driver**

## Analog vs. Microwave Circuit Design

#### Analog

**Differential amps**

Dc-coupled broadband

Resistive and active matching

I, V, impedance

#### Microwave

Single-ended amps

AC-coupled, tuned (narrow band) or distributed (broadband)

Reactive matching (L, C or transmission lines)

S params, Smith chart

Harmonic Fourier Analysis

Differential tuned and broadband circuits

Resistive, active, and reactive matching

Common mode, differential mode, and single-ended mode gain, impedance, matching and stability

#### Outline

•Analog vs. Microwave Circuit Design

- Impedance matching

- Tuned circuit topologies

- Techniques to maximize bandwidth

- Challenges in differential HF circuits

- Nonlinear Techniques

# Why do we need impedance matching at HF?

•Distance between circuit pads and external terminations ~  $\lambda$ . Impedance mismatches at either end cause reflections

- •Need maximum power transfer from source to load

- •Typical matching impedance

- 50  $\Omega$  per side (SE),

- 100  $\Omega$  diff-mode, and

- 25  $\Omega$  in CM.

### Why not at LF?

- •Circuits small compared to wavelength

- •Can afford to lose power since transistors have lots of gain

- •Resistive matching is used to avoid large area caps and inductors

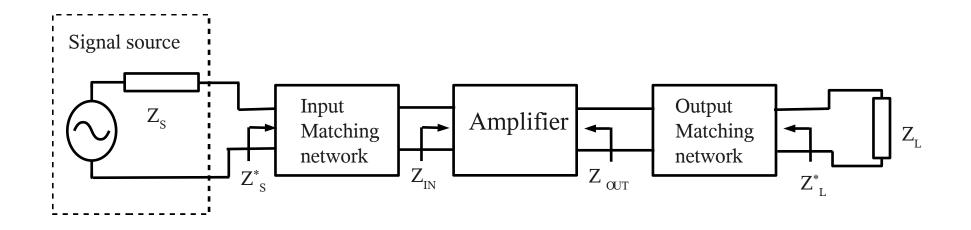

### **Concept of Impedance Matching**

# Narrow-band tuned matching networks

Input/output of transistors look like parallel or series R-C circuits.

- •L-network matching:

- With lumped components

- With transmission lines

- •Multi-section matching

- •Transformer matching

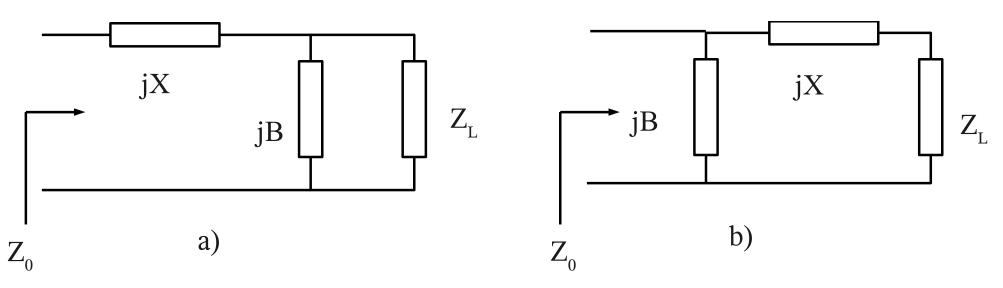

#### **L-Section matching**

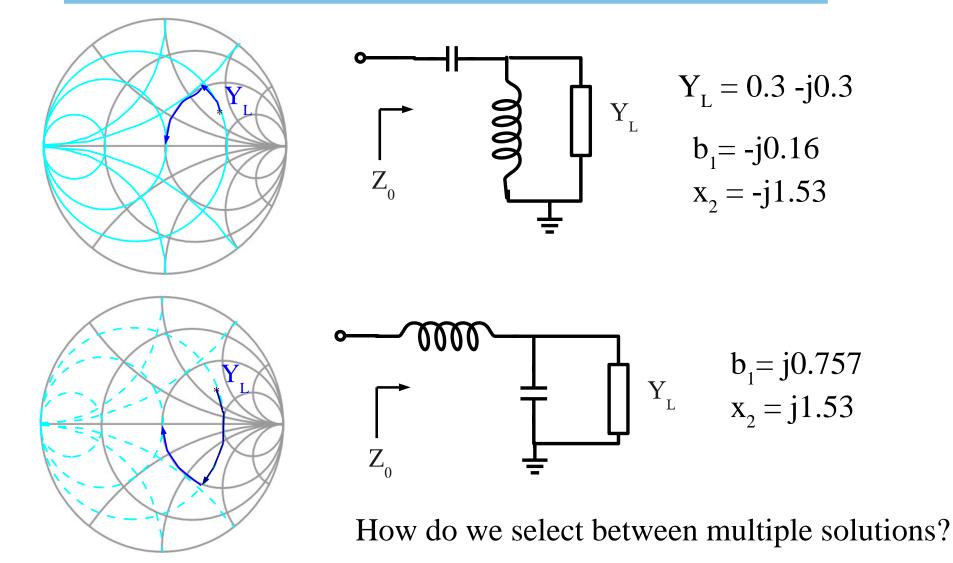

Two lumped or t-line components can match any impedance with non-zero real part to  $Z_{o}$

- Series jX, shunt jB used when  $z_i$  is inside 1+jx circle

- Shunt jB, series jX used when  $z_i$  is outside 1+jx circle

#### L-section matching (ii)

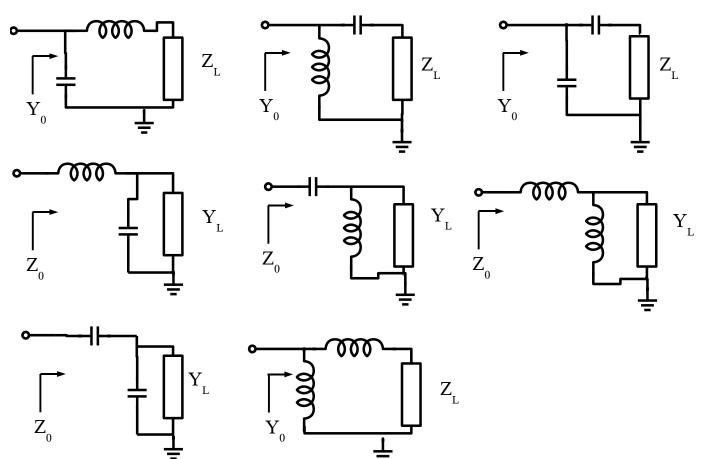

- 8 possible matching circuits exist

- Exact analytical and graphical solutions

### **Example YZ-Smith Chart: z<sub>L</sub>:inside 1+jx circle**

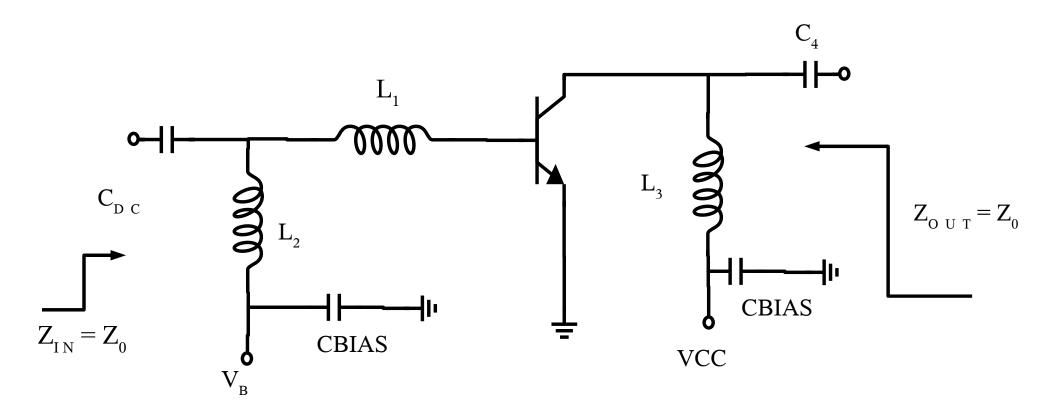

#### **Example: 120-GHz HBT amplifier**

# Q and BW<sub>3dB</sub> of L-section matching network

L-sections are 2<sup>nd</sup> order (two-pole) LPF or HPF networks

- Node Q:  $Q_n = \frac{|B_P|}{C}$   $Q_n = \frac{|X_S|}{R_s}$

- Loaded Q

- Bandwidth

$$Q_{L} = \frac{f_{0}}{BW_{3dB}} = \frac{Q_{n}}{2}$$

Two typical scenarios encountered in practice:

- High Q matching in PAs

- High bandwidth matching

In either case you need more matching elements, not just 2 as in L-section: 2-step L-section,  $\pi$ , and T-networks

## Lossless broadband input/output matching

Higher-order lossless filter networks can be employed to maximize the matching bandwidth.

Ultimate limitation for broadband matching with "lumped" elements is given by the *Bode-Fano limit*.

**Example:** For parallel R-C load:

$$\int_{0}^{\infty} \ln \frac{1}{\left|S_{11}(\omega)\right|} d\,\omega \leq \frac{\pi}{RC}$$

Using t-coils and distributed amplifier topology one can overcome this limit

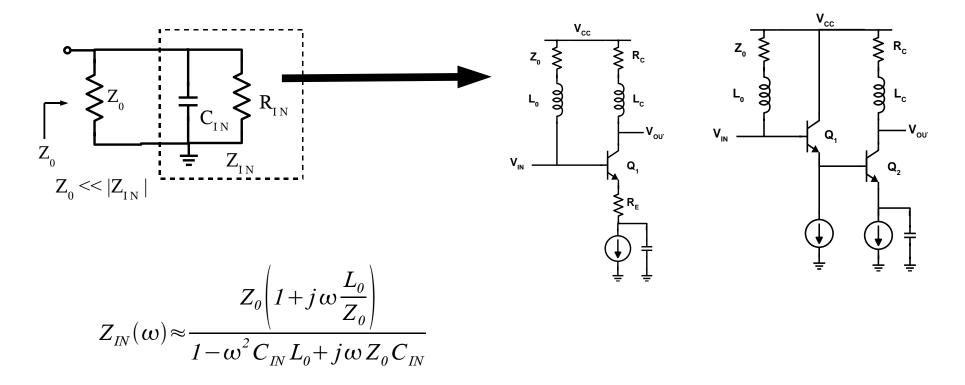

# Lossy broadband input matching techniques

- Brute force

- Negative feedback

#### Lossy matching: Brute force

Add  $Z_{o}$  resistor in parallel with high impedance input/output. Use series inductor to tune out input capacitance

#### Lossy matching: negative feedback

TIA input: low-noise, low-current, large bandwidth

$$Z_{IN}(\omega) = \frac{Z_F}{A+1} \frac{1}{1+j\omega \frac{Z_F C_{IN}}{A+1}}$$

#### Outline

- •Analog vs. Microwave Circuit Design

- Impedance matching

- Tuned circuit topologies

- Techniques to maximize bandwidth

- •Challenges in differential HF circuits

- Nonlinear Techniques

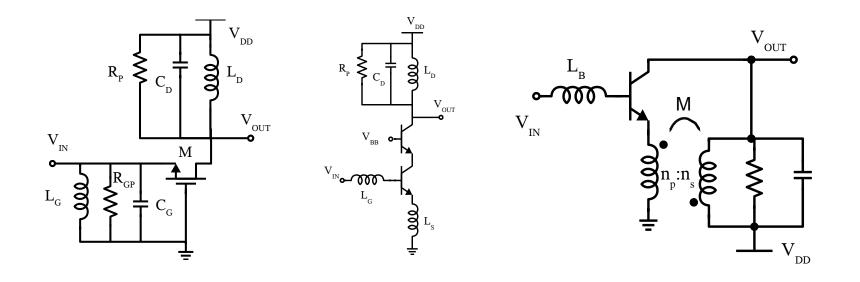

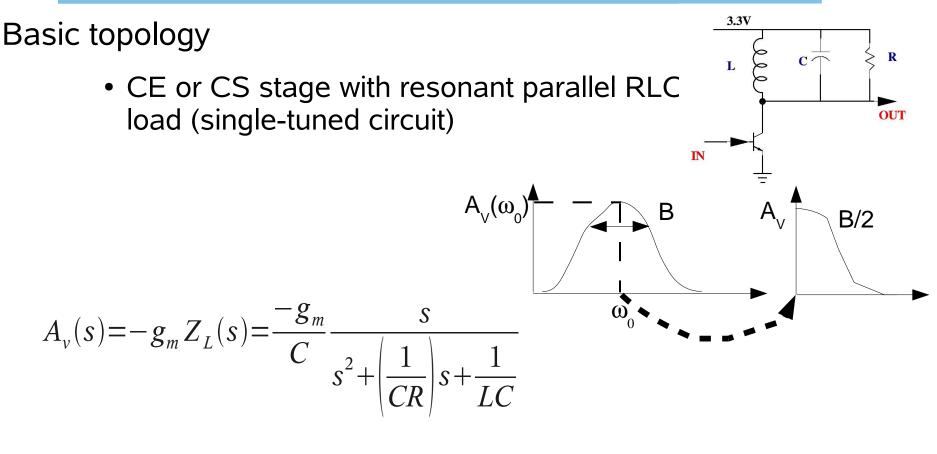

# **Tuned circuit topologies**

Topologies:

- Tuned amplifier with parallel resonant tanks at input and output (CE/CS, CB/CG) (PAs, LNAs)

- Tuned amplifier with series resonance at input and parallel resonance at output (LNA with inductive degeneration)

- Tuned amplifiers with selective negative feedback

## Analysis techniques for tuned circuits

Two-step analysis technique

- Match input/output circuit at "resonant" frequency  $f_o$

- Analyze circuits at resonant frequency f<sub>o</sub> by shifting entire frequency response to DC.

Apply the same methodology as in DC amplifiers to calculate midband gain, input and output impedance

Q of resonant circuits and  $f_o$  dictate gain bandwidth

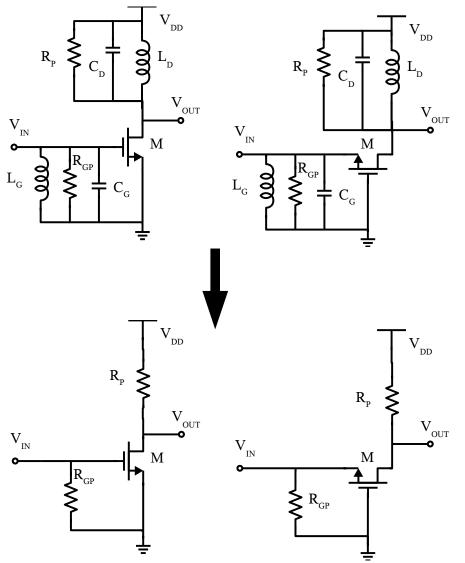

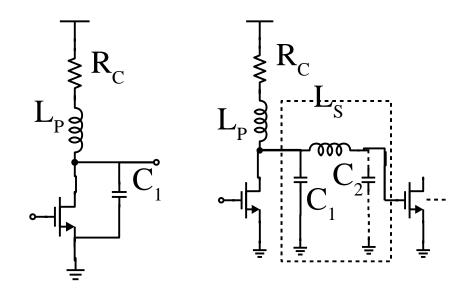

### **Example of single-tuned amplifier analysis**

$$A_v(\omega_0) = -g_m R$$

where  $\omega_0 = \frac{1}{\sqrt{LC}}$ ;  $Q = \omega_0 C R$  and  $B = \frac{1}{CR}$

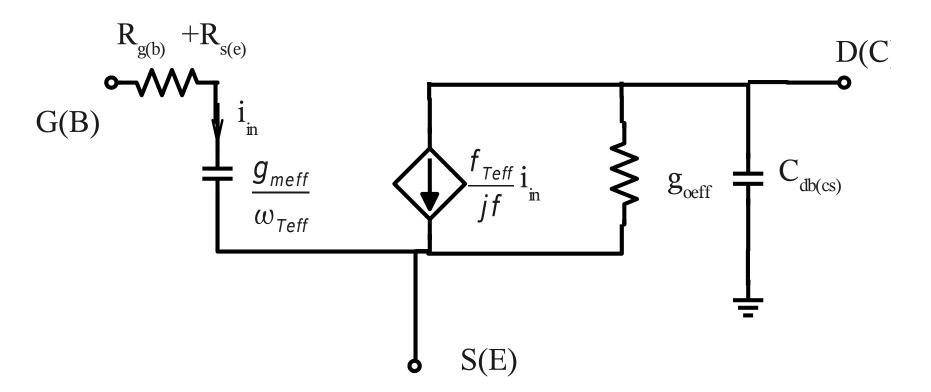

## Simplified FET/HBT circuit for analysis

- Useful in CE/CS configuration

- No Miller capacitance

### Ex. 1: at f they simplify to...

- • $i_{sc}(f_o) = (+/-)g_m V_{in}$ • $Z_{OUT}(f_o) = R_p$  (includes  $r_o$ , loss resistance of  $L_{D}$ )

- • $R_{IN}(f_o) = R_{GP}$  (includes  $R_a$ , loss resistance of  $L_c$ )

$$\bullet A_v(f_o) = i_{sc} \times R_{out} = (+/-)g_m R_p$$

#### Ex. 1: Power gain calculation (ii)

Input and output- matched CS or ac-coupled cascode stage: R<sub>in</sub>

Prove that, for an input and output matched CG stage the power gain is the same as above!

What does it mean?

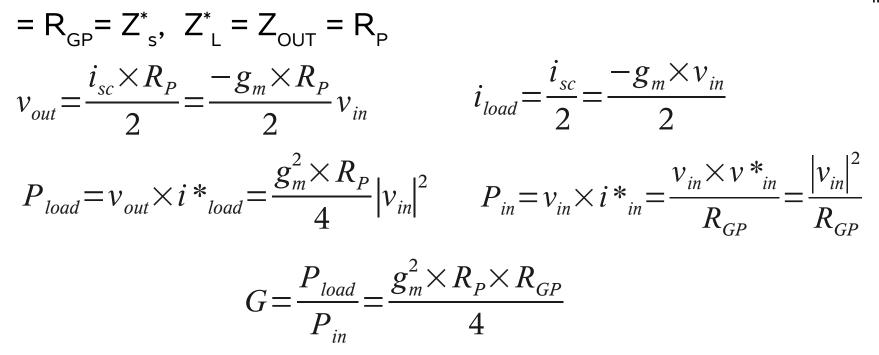

### Ex. 2: Tuned CE/CS or cascode stage with inductive degeneration

- •Series resonance at input

- •Parallel resonance at output

- •Used in LNAs, mixers

#### **Example 2: Continued**

•Account for

$$R_s$$

in  $C_{gs}$ ,  $g_m$ ,  $g_o$ ,  $f_T$

•Transfer  $C_{gd}$  in parallel with  $C_{gs}$

•Replace  $C_{gseff} + C_{gd}$  with  $g_{meff}/\omega_{Teff}$

**Step 1**: Calculate input impedance

$$Z_{in} = R_g + R_s + \omega_{Teff} L_s + j \left[ \omega (L_G + L_s) - \frac{\omega_{Teff}}{\omega g_{meff}} \right]$$

**Step 2**: Calculate output short-circuit current  $i_{sc}$

$$i_{sc} = \frac{-f_{Teff}}{jf} i_{in} = j \frac{f_{Teff}}{f} i_{in}$$

#### Example 2: (iii)

**Step 3:** Match the input impedance to  $Z_0$  and terminate (match) the output on  $R_P$

$$Z_0 = R_{IN} = R_s + R_g + \omega_{Teff} \times L_s$$

and  $Z_L = R_p$

**Step 4:** Calculate the current in load ( $R_P$ ) and output power

$$i_{load} = \frac{i_{sc}}{2} = \frac{-f_{Teff}}{2jf} i_{in} \qquad v_{out} = \frac{i_{sc} \times R_P}{2} = \frac{-f_{Teff} \times R_P}{2jf} i_{in}$$

$$P_{in} = v_{in} \times i_{in}^* = i_{in} \times R_{IN} \times i_{in}^* = R_{IN} |i_{in}|^2$$

$$G = \frac{P_{load}}{P_{in}} = \frac{f_{Teff}^2}{4f^2} \times \frac{R_P}{R_{IN}}$$

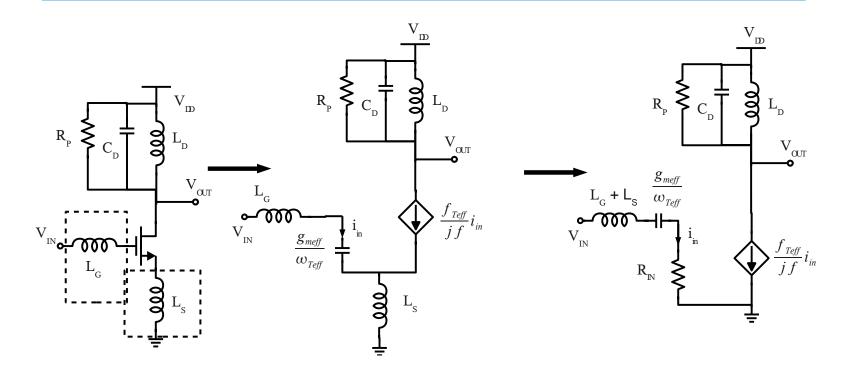

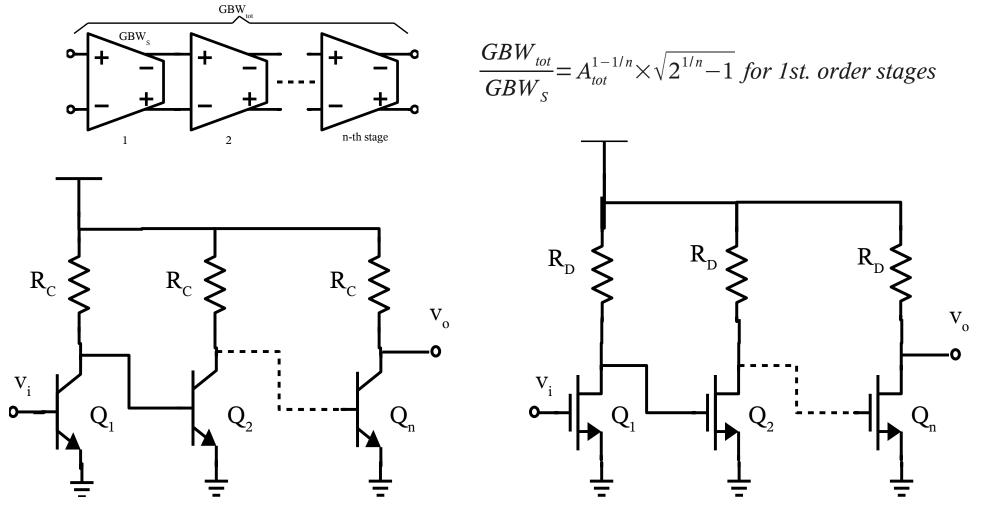

#### Topologies and techniques to maximize circuit bandwidth

BW decreases as number of cascaded stages increases

#### **Technique to analyze bandwidth**

Open time constant technique (Elmore delay)

Allows to calculate dominate pole with reasonable approximation

# How to improve circuit bandwidth?

- •Use faster transistors

- •Use broadband circuit topologies and techniques

- Reduce the input capacitance of the amplifier stage

- Cherry-Hooper stage

- Buffering and scaling of stages

- Use inductive peaking and distributed amp. topologies

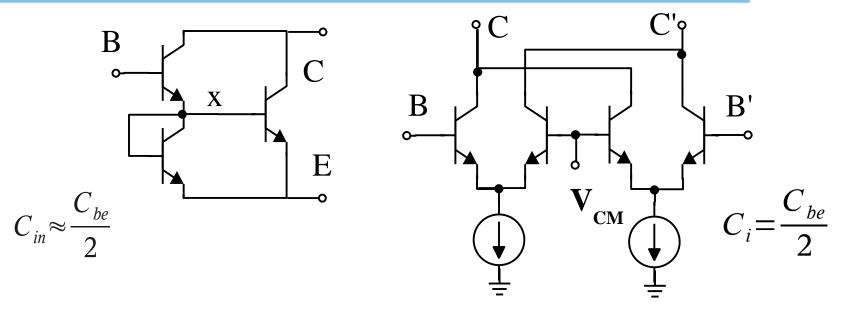

# **Reducing input capacitance: f<sub>-</sub> doubler**

- Useful if current gain rather than power gain is important

- Works well if  $C_{be}(C_{gs}) >> C_{bc}, C_{cs}(C_{gd}, C_{db})$

- Efficient in HBT implementation but consumes more power

- MOSFET implementation suffers from additional  $C_{db}^{}$ ,  $C_{sb}^{}$

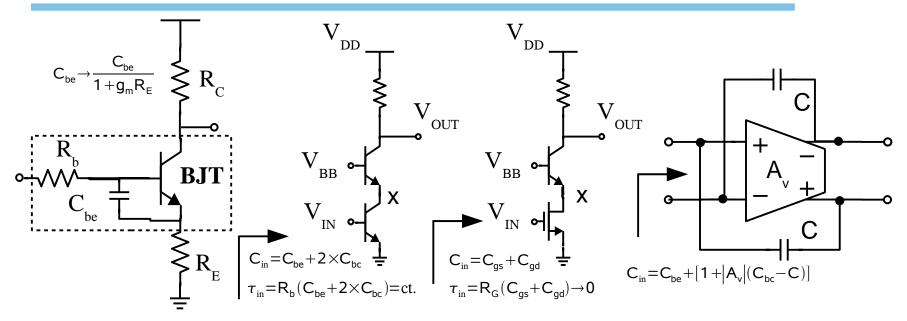

# Reducing input capacitance (ii)

- a) Series resistive feedback (emitter degeneration)

- b) Reduce Miller capacitance with cascode (HBT > MOS)

- c) Reduce Miller and  $R_q \times C_{in}$  with BiCMOS cascode

- d) Cancel out Miller cap with positive feedback (dangerous)

- e) Combinations of all of the above

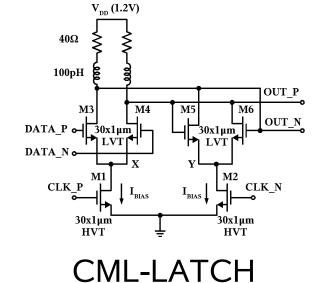

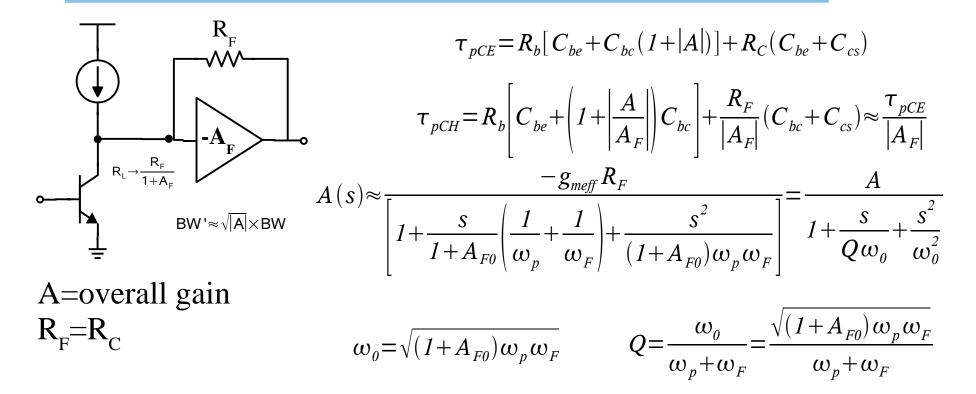

### Speed-up input & output poles: Cherry-Hooper

•Bipolar implementation is common but requires high (3.3V and up) power supply (1.8-V possible in SiGe BiCMOS)

•1.2 V CMOS implementations possible (3-stacked LVT FETS)

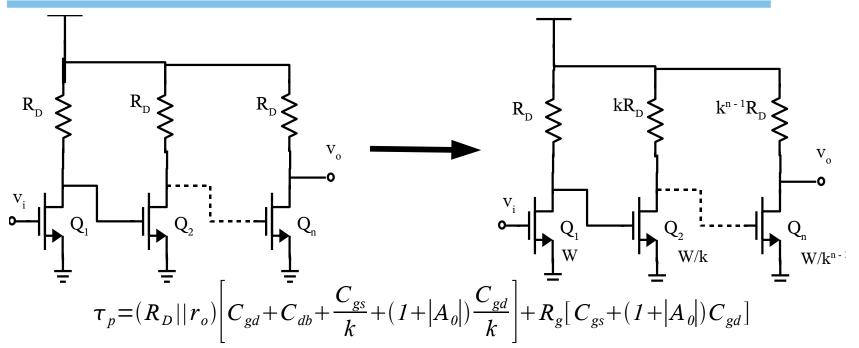

## (Buffering) and Scaling

- Reduce output node capacitance by decreasing the bias current and size of each following stage

- Works in input amplifier of broadband receivers but limited by minimum size transistor

- Buffering works in BJT circuits by using EF+ INV

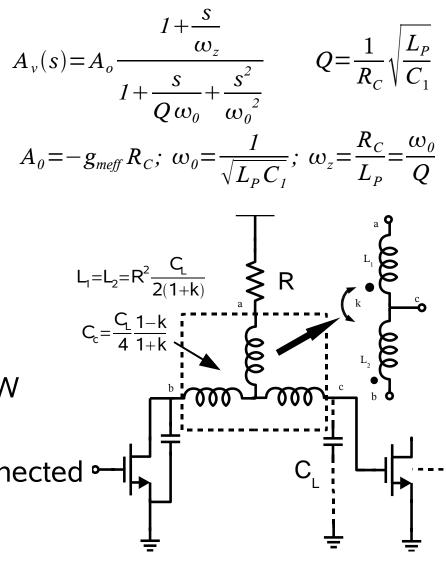

#### Tune out node cap: inductive peaking (1930's)

- a) Shunt peaking: about 1.6xBW

- b) Shunt-series peaking: about 2xBW

- c) Shunt and double-series, t-coil >

2.8xBW (T. Lee, 1998). C<sub>c</sub> is connected ∽

between nodes a and b.

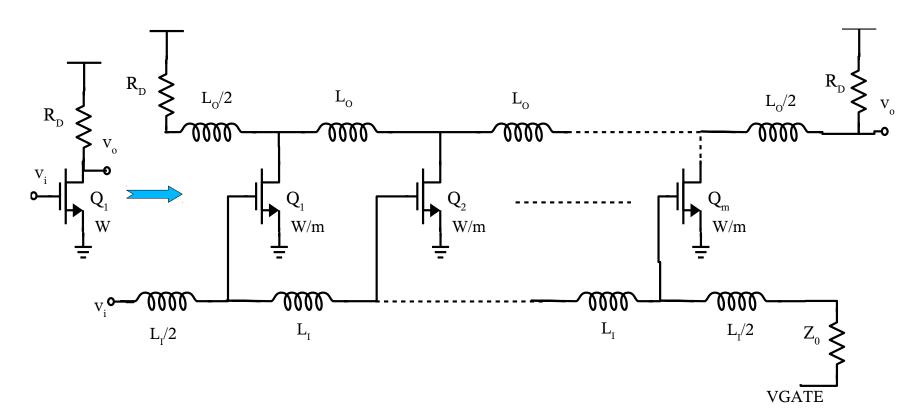

### **Distributed amplifier**

Absorb input and output capacitance in artificial t-line Parcival 1936

## **Distributed amplifier**

$$Z_0 = \sqrt{\frac{L}{C}} \text{ and } BW_{3dB} = \frac{1}{\pi \sqrt{LC}}$$

$$L_I = Z_0^2 \frac{C_I}{m}$$

and  $L_O = R_D^2 \frac{C_O}{m}$

$$GBW_{S} = \frac{g_{meff}}{2\pi (C_{I} + C_{O})}$$

$$GBW'_{S} = min\left(m\frac{g_{meff}}{2\pi C_{I}}, m\frac{g_{meff}}{2\pi C_{O}}\right)$$

$$A = -m \frac{g_{meff}}{m} \frac{R_D}{2} = -g_{meff} \frac{R_D}{2}$$

$$BW_{3dB} = min \left( \frac{1}{\pi \sqrt{L_I \frac{C_I}{m}}}, \frac{1}{\pi \sqrt{L_O \frac{C_O}{m}}} \right)$$

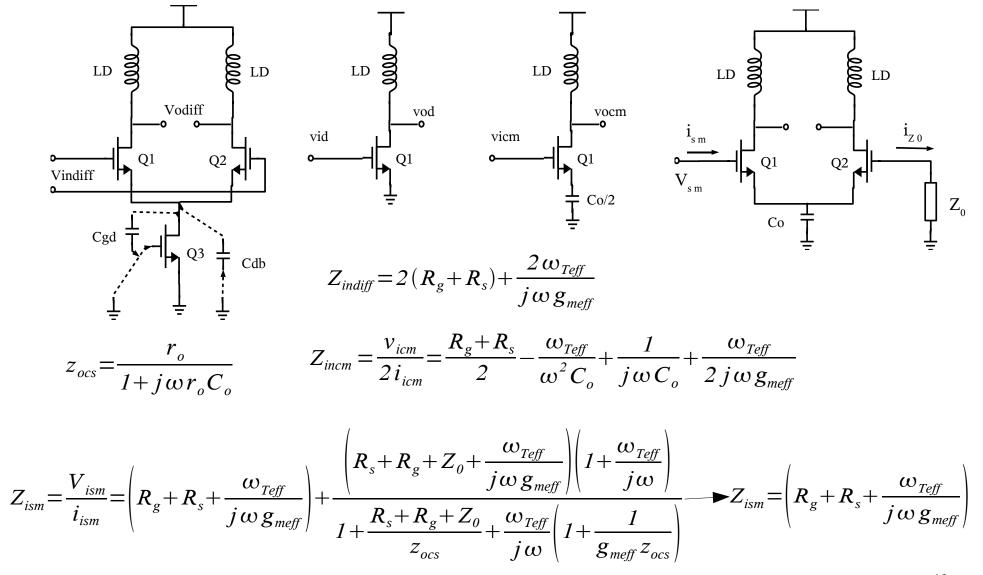

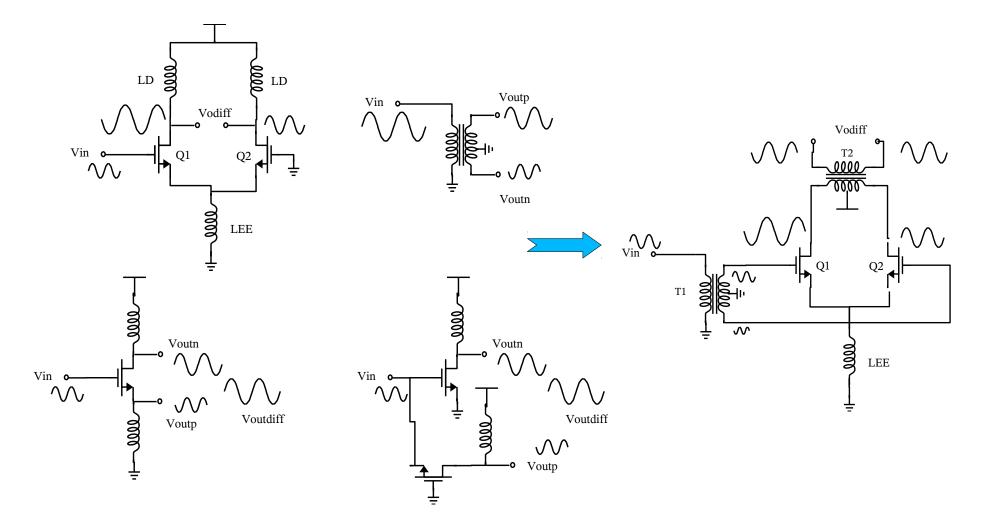

## Challenges in diff. circuits at HF

•No common mode rejection (current sources are capacitive, especially the "advanced" ones)

•The differential pair transistors are capacitively degenerated in common-mode leading to additional stability problems.

•Coupling between differential inputs due to capacitive input impedance.

•Differential impedance is no longer 2×single-ended impedance.

# How to verify stability

In single-ended, differential, and common mode check for:

- •k < 1 at any port

- $\bullet S_{ii} > 1$  at any port i

- negative resistance at any port

- •peaking > 1dB in gain vs. frequency characteristics

- •check for any of the above between stages if suspicious...

- •In amplifiers with feedback, check for the closed loop phase margin (>60°) in DM, CM, and SE mode.

## **Common reasons for instability**

Diff/Common mode negative resistance problem

- •Capacitively loaded emitter/source -> negative resistance

- •Monolithic inductors turn into capacitors beyond SRF

- •Current tails are capacitive: negative resistance in common mode

- •Cascode bipolar and CMOS circuits are unstable

- •Resistive degeneration helps.

- Inductive supply lines

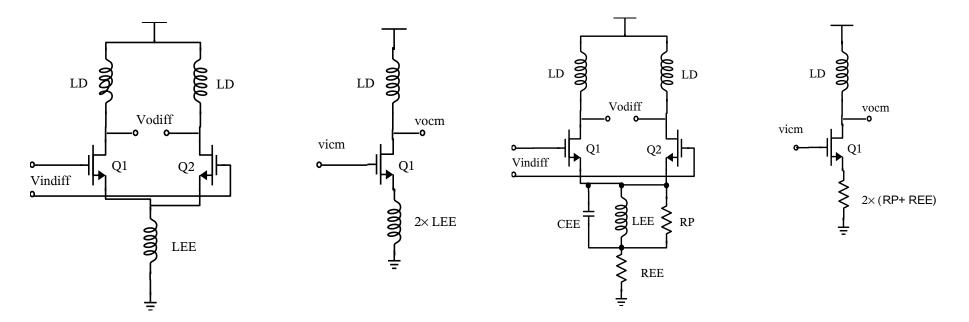

#### SE, DM, CM input impedance in diff. pair

42

## **Techniques to improve CMR at HF**

#### CM leakage at HF and solutions

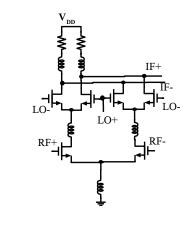

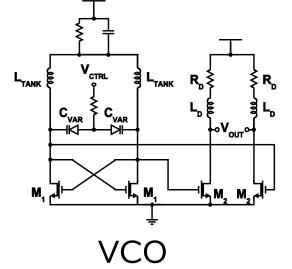

## Non-linear techniques

- Most important HF circuits operate at large signal:

- PA,

- multiplier,

- Mixer,

- Oscillator

- Harmonic Fourier series analysis is employed to analyze such circuits.

$I_{c}(t) = I_{0} + I_{1}\cos(\omega t) + I_{2}\cos(2\omega t) + ... + I_{n}\cos(n\omega t)$

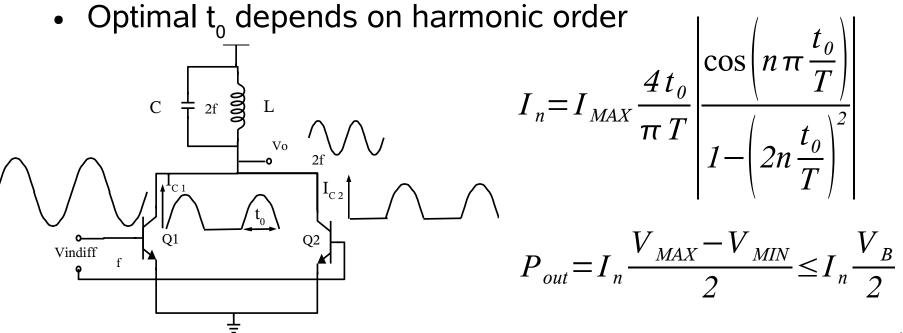

### **Multipliers**

- Important in synthesizers and signal sources >100 GHz

- I<sub>MAX</sub> = maximum collector/drain current of transistor

- T = period of fundamental signal at input

- $t_{o}$ <T/2 is duration of current pulse => class AB to B

# **Design equations**

$$R_{LOPT} = \frac{V_{MAX} - V_{MIN}}{2I_n} \approx \frac{V_{DD}}{I_n}$$

$$P_{out} = I_n \frac{V_{MAX} - V_{MIN}}{2} \le I_n \frac{V_B}{2}$$

$$I_0 = I_{MAX} \frac{2t_0}{\pi T}$$

$$P_{DC} = 2I_0 V_{DD} = \frac{4t_0}{\pi T} I_{MAX} V_{DD}$$

$$\eta_{DC} = \frac{P_L}{P_{DC}} \le \frac{I_n}{2I_0} = \left| \frac{\cos\left(n\pi \frac{t_0}{T}\right)}{1 - \left(2n\frac{t_0}{T}\right)^2} \right|$$

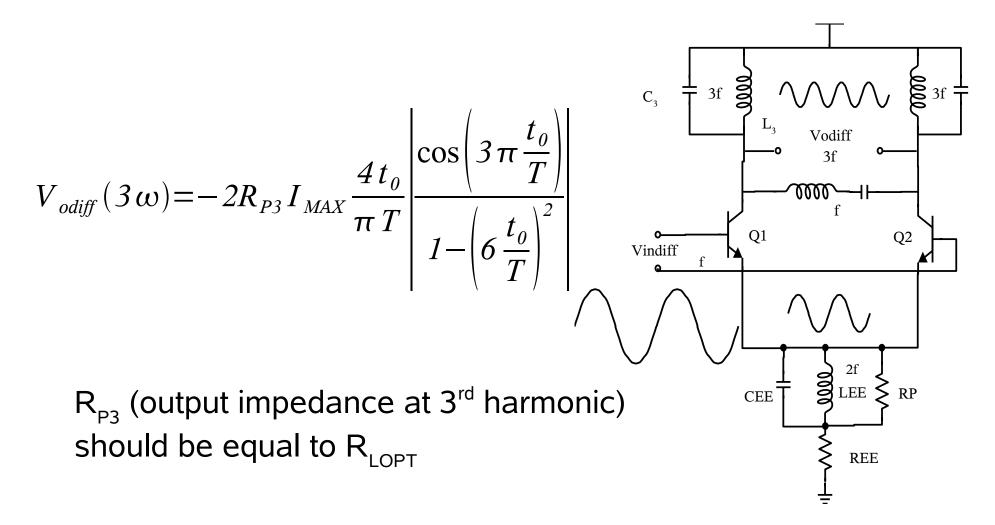

## **Tripler**

#### Summary

- HF circuit topologies feature L, xfmr, t-lines

- Impedance matching critical at HF

- Tuned HF circuits can be analyzed using "downconversion" and applying traditional LF amplifier analysis

- Broadbanding techniques involve special topologies, feedback, scaling, inductive peaking

- Differential and common-mode stability analysis critical in successful HF ICs

- Nonlinear circuits are analyzed using Fourier series